动态欠压锁定检测电路及集成电路的制作方法

本申请涉及模拟电路,具体而言,涉及一种动态欠压锁定检测电路及集成电路。

背景技术:

1、传统的欠压锁定(undervoltage lockout,uvlo)检测电路一般是基于固定电压阈值进行检测。示例的,图1为传统的uvlo检测电路的示意图,如图1所示,电源电压vccb通过分压电路和固定基准电压vref进行比较,如果电源电压vccb低于某一固定值,分压电路的输出电压低于固定基准电压vref,比较器输出高电平,从而控制芯片的行为,例如复位或者关闭整个芯片的功能。

2、但是传统的uvlo检测电路在电源电压vccb下降较快时,uvlo检测电路的输出信号无法及时有效控制芯片的行为,使芯片在实际应用中的灵活性不够,鲁棒性不强。

技术实现思路

1、本申请的目的在于,针对上述现有技术中的不足,提供一种动态欠压锁定检测电路及集成电路,以便输出跟随电源电压变化比例保持固定的动态欠压锁定信号,提高芯片的应用灵活度和鲁棒性。

2、为实现上述目的,本申请实施例采用的技术方案如下:

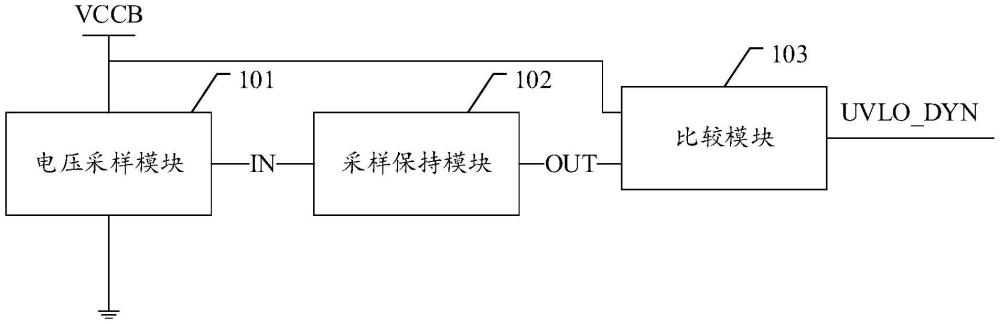

3、第一方面,本申请实施例提供了一种动态欠压锁定检测电路,所述动态欠压锁定检测电路包括:电压采样模块、采样保持模块和比较模块;

4、预设电源通过所述电压采样模块接地,用于对所述预设电源进行电压采样得到采样电压;

5、所述采样保持模块的输入端连接所述电压采样模块,用于对所述采样电压进行保持,并输出采样保持电压;

6、所述比较模块的正输入端连接所述采样保持模块的输出端,所述比较模块的负输入端连接所述预设电源,所述比较模块用于对所述电源电压和所述采样保持电压进行比较,生成并向预设芯片输出动态欠压锁定信号。

7、在一种可能的实现方式中,所述采样保持模块包括:开关单元和第一电容;

8、所述开关单元的第一端作为所述采样保持模块的输入端,所述开关单元的第二端连接所述第一电容的一端作为所述采样保持模块的输出端,所述第一电容的另一端接地,所述开关单元的控制端连接预设时钟电路。

9、在一种可能的实现方式中,所述采样保持模块包括:输入导通单元、输出导通单元以及第二电容;

10、所述输入导通单元的第一端作为所述采样保持模块的输入端,所述输入导通单元的第二端通过所述第二电容接地,所述输入导通单元的第二端还连接所述输出导通单元的第一端,所述输出导通单元的第二端为所述采样保持模块的输出端。

11、在一种可能的实现方式中,所述输入导通单元为第一三极管,所述第一三极管的发射极作为所述输入导通单元的第一端,所述第一三极管的基极连接所述第一三极管的集电极作为所述输入导通单元的第二端;或者,

12、所述输入导通单元为:第一mos管,所述第一mos管的源极作为所述输入导通单元的第一端,所述第一mos管的栅极连接所述第一mos管的漏极作为所述输入导通单元的第二端。

13、在一种可能的实现方式中,所述输出导通单元包括:偏置单元和开关管;

14、所述偏置单元的一端连接所述预设电源,所述开关管的第一端作为所述输出导通单元的第一端,所述偏置单元的另一端连接所述开关管的第二端作为所述输出导通单元的第二端,所述开关管的第三端接地。

15、在一种可能的实现方式中,所述偏置单元包括:第二三极管和电阻;

16、所述第二三极管的发射极作为所述偏置单元的一端,所述第二三极管的集电极连接所述电阻的一端,所述第二三极管的基极连接所述第二三极管的集电极,所述电阻的另一端作为所述偏置单元的另一端;或者,

17、所述偏置单元包括:第二mos管和电阻;

18、所述第二mos管的漏极作为所述偏置单元的一端,所述第二mos管的源极连接所述电阻的一端,所述第二mos管的栅极连接所述第二mos管的源极,所述电阻的另一端作为所述偏置单元的另一端。

19、在一种可能的实现方式中,所述开关管为第三三极管,所述第三三极管的基极作为所述开关管的第一端,所述第三三极管的发射极作为所述开关管的第二端,所述第三三极管的集电极作为所述开关管的第三端;或者,

20、所述开关管为第三mos管,所述第三mos管的栅极作为所述开关管的第一端,所述第三mos管的源极作为所述开关管的第二端,所述第三mos管的漏极作为所述开关管的第三端。

21、在一种可能的实现方式中,所述动态欠压锁定检测电路还包括:上电检测模块和延迟模块;

22、所述上电检测模块的输入端连接所述电压采样模块,所述上电检测模块的输出端通过所述延迟模块连接所述比较模块的使能端,用于根据所述采样电压控制所述比较模块的工作状态。

23、在一种可能的实现方式中,所述上电检测模块包括:比较器;

24、所述比较器的正输入端作为所述上电检测模块的输入端,所述比较器的负输入端用于输入预设电压阈值,所述比较器的输出端作为所述上电检测模块的输出端。

25、第二方面,本申请实施例还提供一种集成电路,所述集成电路包括:如第一方面任一项所述的动态欠压锁定检测电路和芯片;

26、所述动态欠压锁定检测电路连接所述芯片中逻辑电路的控制端,所述逻辑电路根据所述动态欠压锁定检测电路输出的动态欠压锁定信号进行控制。

27、本申请的有益效果是:

28、本申请提供的动态欠压锁定检测电路及集成电路,在电源电压下电的过程中,控制作为参考电压的采样电压与电源电压成比例关系并保持一段时间,以便可以及时有效地控制芯片的信号传输通道有序关闭;且通过控制参考电压跟随电源电压变化,以输出跟随电源电压变化比例保持固定的动态欠压锁定信号,可以提高芯片在实际应用中的灵活性和鲁棒性。

技术特征:

1.一种动态欠压锁定检测电路,其特征在于,所述动态欠压锁定检测电路包括:电压采样模块、采样保持模块和比较模块;

2.根据权利要求1所述的动态欠压锁定检测电路,其特征在于,所述采样保持模块包括:开关单元和第一电容;

3.根据权利要求1所述的动态欠压锁定检测电路,其特征在于,所述采样保持模块包括:输入导通单元、输出导通单元以及第二电容;

4.根据权利要求3所述的动态欠压锁定检测电路,其特征在于,所述输入导通单元为第一三极管,所述第一三极管的发射极作为所述输入导通单元的第一端,所述第一三极管的基极连接所述第一三极管的集电极作为所述输入导通单元的第二端;或者,

5.根据权利要求3所述的动态欠压锁定检测电路,其特征在于,所述输出导通单元包括:偏置单元和开关管;

6.根据权利要求5所述的动态欠压锁定检测电路,其特征在于,所述偏置单元包括:第二三极管和电阻;

7.根据权利要求5所述的动态欠压锁定检测电路,其特征在于,所述开关管为第三三极管,所述第三三极管的基极作为所述开关管的第一端,所述第三三极管的发射极作为所述开关管的第二端,所述第三三极管的集电极作为所述开关管的第三端;或者,

8.根据权利要求1所述的动态欠压锁定检测电路,其特征在于,所述动态欠压锁定检测电路还包括:上电检测模块和延迟模块;

9.根据权利要求8所述的动态欠压锁定检测模块,其特征在于,所述上电检测模块包括:比较器;

10.一种集成电路,其特征在于,所述集成电路包括:如权利要求1-9任一项所述的动态欠压锁定检测电路和芯片;

技术总结

本申请提供一种动态欠压锁定检测电路及集成电路,涉及模拟电路技术领域。该动态欠压锁定检测电路包括:电压采样模块、采样保持模块和比较模块;预设电源通过电压采样模块接地,用于对预设电源进行电压采样得到采样电压;采样保持模块的输入端连接电压采样模块,用于对采样电压进行保持,并输出采样保持电压;比较模块的正输入端连接采样保持模块的输出端,比较模块的负输入端连接预设电源,比较模块用于对电源电压和采样保持电压进行比较,生成动态欠压锁定信号。本申请可以输出跟随电源电压变化比例保持固定的动态欠压锁定信号,提高芯片的应用灵活度和鲁棒性。

技术研发人员:段新东,卿健

受保护的技术使用者:成都市易冲半导体有限公司

技术研发日:

技术公布日:2024/11/14

技术研发人员:段新东,卿健

技术所有人:成都市易冲半导体有限公司

备 注:该技术已申请专利,仅供学习研究,如用于商业用途,请联系技术所有人。

声 明 :此信息收集于网络,如果你是此专利的发明人不想本网站收录此信息请联系我们,我们会在第一时间删除