一种实现FPGA程序定期自检和自修复的方法与流程

本发明属于航空、航天及核电领域中的fpga高可靠性设计,具体涉及一种实现fpga程序定期自检和自修复的方法。

背景技术:

1、随着信息技术的发展,fpga能够实现的功能日益丰富,应用场景也越来越复杂多样。在一些特殊的应用环境如辐射源附近、宇宙空间中,需要定期对fpga程序进行自检和自动纠错,以确保系统鲁棒性和功能正确性。

2、常规的自检方式是将fpga外部程序存储器中的数据全部读取出来,通过crc等方法与校验码对比校验。优点是占用的存储空间小;缺点是一旦发现问题只能上报,无法实现自修复。

技术实现思路

1、(一)要解决的技术问题

2、本发明要解决的技术问题是如何提供一种实现fpga程序定期自检和自修复的方法,以解决高辐照环境下fpga器件长期可靠运行及自检和自动纠错问题。

3、(二)技术方案

4、为了解决上述技术问题,本发明提出一种实现fpga程序定期自检和自修复的方法,该方法包括:

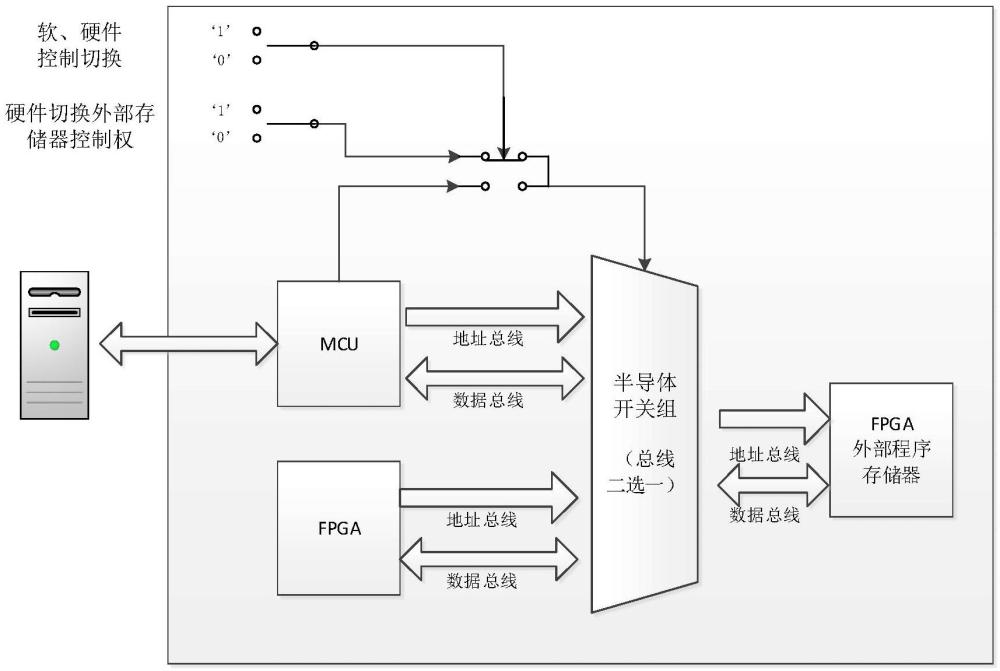

5、设置切换开关:在fpga、mcu和fpga外部程序存储器之间增加半导体总线切换开关;通过mcu控制半导体总线切换开关,用于切换对fpga外部程序存储器的控制权,当mcu选通控制引脚输入为“1”时,fpga外部程序存储器与mcu直连;当mcu选通控制引脚输入为“0”时,fpga外部程序存储器与fpga直连;

6、存储器分区:将fpga外部程序存储器按地址分为上下两个区,分别存储同样的fpga程序;

7、加电启动:每次设备加电启动时默认fpga外部程序存储器与fpga联通,用于加载fpga程序,加载完成后正常运行预定功能;

8、定期自检:定期自检时,由mcu切换fpga外部程序存储器控制权;通过mcu直接访问fpga外部程序存储器,对其上下两个半区的数据进行逐字读取和比对,若一致,则自检通过,上报日志,并回到正常运行模式;若不一致,则上报故障日志,通过两个半区内存储的相应校验码进行进一步故障定位,确认故障半区后,通过无故障半区内存储的fpga程序对故障半区进行覆盖,再次进行校验,无误后上报处理结果,回到正常运行模式。

9、(三)有益效果

10、本发明提出一种实现fpga程序定期自检和自修复的方法,本发明通过mcu在定期自检期间直接访问fpga外部程序存储器,对其上下两个半区的数据进行逐字读取和比对,在尽量少占用mcu资源的情况下实现最高的自检效率。并且,一旦发现fpga程序中出现单粒子翻转,可通过无故障分区对对故障分区进行修复。

11、本发明为高辐照环境下fpga器件长期可靠运行(主要是抵御单粒子翻转seu)提供一种新的解决问题思路和方法。意在通过定期自检提前发现seu问题,并及时进行自动修复。

12、本发明提高fpga外部存储器利用率和fpga程序定期自检的效率和可靠性。

技术特征:

1.一种实现fpga程序定期自检和自修复的方法,其特征在于,该方法包括:

2.如权利要求1所述的实现fpga程序定期自检和自修复的方法,其特征在于,所述半导体总线切换开关为单刀双掷模拟开关。

3.如权利要求1所述的实现fpga程序定期自检和自修复的方法,其特征在于,所述半导体总线切换开关为cd4052、bct4157或hs102。

4.如权利要求1所述的实现fpga程序定期自检和自修复的方法,其特征在于,在mcu与总线切换开关之间增加硬件拨码开关,当硬件拨码开关高位设置为0时,由硬件拨码开关控制;当硬件拨码开关高位设置为1时,由mcu控制。

5.如权利要求4所述的实现fpga程序定期自检和自修复的方法,其特征在于,若由硬件控制,mcu选通控制引脚设置无效;当硬件拨码开关低位设置为0时,控制半导体总线切换开关将fpga与fpga外部存储器直连,此时,fpga实现日常的程序加载和逻辑功能;当硬件拨码开关低位设置为1时,控制半导体总线切换开关将mcu与fpga外部存储器直连,此时,通过mcu读写fpga外部存储器,实现fpga程序的升级、修复,实现对fpga外部存储器空闲区域的读写,使其作为mcu外部非易失存储器存储空间的补充。

6.如权利要求4所述的实现fpga程序定期自检和自修复的方法,其特征在于,若由mcu控制,硬件拨码开关低位设置无效;当mcu选通控制引脚设置为0时,控制半导体总线切换开关将fpga与fpga外部存储器直连,此时,fpga实现日常的程序加载和逻辑功能;当mcu选通控制引脚设置为1时,控制半导体总线切换开关将mcu与fpga外部存储器直连,此时,通过mcu读写fpga外部存储器,实现fpga程序的升级、修复,实现对fpga外部存储器空闲区域的读写,使其作为mcu外部非易失存储器存储空间的补充。

7.如权利要求1所述的实现fpga程序定期自检和自修复的方法,其特征在于,fpga外部程序存储器内部按地址分为同样大小的两个分区,一个作为主分区,用于启动时为fpga加载程序;一个作为备用分区,与主分区互为备份,用于其中一个分区出现seu故障时通过另一分区进行修复。

8.如权利要求7所述的实现fpga程序定期自检和自修复的方法,其特征在于,除存储fpga程序外,还在各自分区分别存储相应的校验码,用于在出现seu故障时确认故障所在分区。

9.如权利要求1所述的实现fpga程序定期自检和自修复的方法,其特征在于,无论拨码开关硬件还是mcu软件取得对fpga外部程序存储器切换的控制权,在设备加电或重新启动时均默认将fpga与fpga外部程序存储器相连,使上电或程序加载过程中,fpga直接从fpga外部程序存储器的主分区中读取程序并正常运行。

10.如权利要求1-9任一项所述的实现fpga程序定期自检和自修复的方法,其特征在于,mcu接收自检指令后切换fpga外部程序存储器控制权;通过mcu直接访问fpga外部程序存储器,对其上下两个半区的数据进行逐字读取和比对,若一致,则自检通过,上报日志,并回到正常运行模式;若不一致,则上报故障日志,通过两个半区内存储的相应校验码进行进一步故障定位,确认故障半区后,通过无故障半区内存储的fpga程序对故障半区进行覆盖,再次进行校验,无误后上报处理结果,回到正常运行模式;若尝试三次以上无法自修复,则上报严重故障,由现场运维人员通过硬件拨码开关手动处理,并进行全面检修。

技术总结

本发明涉及一种实现FPGA程序定期自检和自修复的方法,属于航空、航天及核电领域中的FPGA高可靠性设计技术领域。本发明在FPGA、MCU和FPGA外部程序存储器之间增加半导体总线切换开关,默认由MCU控制半导体总线切换开关的切换选通使能;将FPGA外部程序存储器按地址分为上下两个区,分别存储同样的FPGA程序;每次设备加电启动时默认FPGA外部程序存储器与FPGA联通,用于加载FPGA程序;定期自检时,由MCU切换FPGA外部程序存储器控制权,通过MCU直接访问FPGA外部程序存储器进行自检。本发明能通过定期自检提前发现SEU问题,并及时进行自动修复,提高了FPGA外部存储器利用率和FPGA程序定期自检的效率和可靠性。

技术研发人员:吴飞,宋科,李校南,高连跃,张兴凯,吴志轩,任凯琦,贾俊峰,张明明,赵博文,王法秀

受保护的技术使用者:北京计算机技术及应用研究所

技术研发日:

技术公布日:2024/11/14

技术研发人员:吴飞,宋科,李校南,高连跃,张兴凯,吴志轩,任凯琦,贾俊峰,张明明,赵博文,王法秀

技术所有人:北京计算机技术及应用研究所

备 注:该技术已申请专利,仅供学习研究,如用于商业用途,请联系技术所有人。

声 明 :此信息收集于网络,如果你是此专利的发明人不想本网站收录此信息请联系我们,我们会在第一时间删除