四端法电阻测试结构的制作方法

本发明涉及半导体集成电路制造领域,特别是涉及一种四端法电阻测试结构。

背景技术:

1、如图1所示,是现有两端法电阻测试结构的电路图;在被测试电阻101的两端分别设置有一个焊垫(pad)且分别用标记102a和102b标出。其中,焊垫102a作为正激励(force,f)端,焊垫102b作为负激励端,图1中,正激励端也采用f+pad表示,负激励端也采用f-pad表示,f+表示正激励,f-表示负激励。现有两端法电阻测试由于有寄生串联电阻的影响,会造成电阻不准确。

2、四端法电阻测量可以有效避免寄生串联电阻的影响,得到准确的测量电阻值。如图2所示,是现有四端法电阻测试结构的电路图;被测试电阻201的每一端都需要连接两个焊垫,共需要连接四个焊垫,四个焊垫分别用标记202a、202b、202c和202d标出。其中,焊垫202a作为f+pad,焊垫102b作为f-pad,焊垫202c作为正测量(sense,s)端,焊垫202d作为负测量端,正测量端也采用s+pad表示,负测量端也采用s-pad表示,s+表示正测量,s-表示负测量。

3、在半导体晶圆电阻测试中,图2所示的现有四端法电阻测量每个电阻结构需要占据四个金属层pad即f+/f-/s+/s-,相比两端法需要更多的pad数量,会占用更多晶圆面积。

4、实际应用中为了综合考虑测试准确性以及结构占用面积,往往是四端法与两端法的结构同时存在。

5、参考图2所示,现有四端法测试的具体设置包括:

6、f+pad即焊垫202a施加激励即force电流或电压,记录或量测下f+pad的电流,记为iforce。

7、f-pad即焊垫202b接地或force零电压

8、s+pad即焊垫202c与s-pad即焊垫202d都force零电流并同时测量电压,分别记为vsensep和vsensen。

9、最后四端法测得电阻值为r=(vsensep-vsensen)/iforce。

10、四端法由于测量的电压由sense端的差值得到,而sense端上电流为零,所以vsense不会有寄生电阻导致的电压降,所以可以测得非常准确的电阻两端电压值从而计算得到准确的电阻值。

11、四端法的最大弊端就是每个电阻结构要占用四个pad,非常消耗测试结构面积。

技术实现思路

1、本发明所要解决的技术问题是提供一种四端法电阻测试结构,能节省焊垫数量从而节省面积。

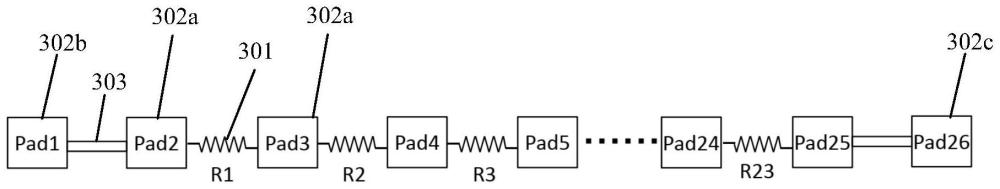

2、为解决上述技术问题,本发明提供的四端法电阻测试结构包括多条测试单元(testkey),各所述测试单元包括:

3、由两个以上被测试电阻串联形成的电阻串,所述电阻串中包括多个焊垫,所述焊垫包括第一焊垫。

4、各所述被测试电阻的两端分别设置有一个第一焊垫,各所述被测试电阻的两个第一焊垫中的至少一个和相邻的所述被测试电阻的第一焊垫共用。

5、各所述被测试电阻都包括两个激励(force)端和两个测量(sense)端,两个激励端由所述被测试电阻的两端的所述第一焊垫形成以及两个所述测量端分别由位于对应的所述激励端相邻位置上的一个焊垫组成。

6、当选定被测试电阻的选定激励端对应的所述第一焊垫和相邻被测试电阻共用时,所述选定被测试电阻的和所述选定激励端相邻的选定测量端由所述相邻被测试电阻的另一端的所述第一焊垫组成。

7、进一步的改进是,所述焊垫还包括第二焊垫和第三焊垫。

8、位于所述电阻串两端的所述被测试电阻分别为第一被测试电阻和最后一个被测试电阻;所述第一个被测试电阻的第一端还设置有一个第二焊垫,所述最后一个被测试电阻的第二端还设置有一个第三焊垫。

9、进一步的改进是,当所述选定被测试电阻为所述第一个被测试电阻时,所述选定被测试电阻的第一端处的所述测量端由所述第二焊垫组成。

10、进一步的改进是,当所述选定被测试电阻为所述最后一个被测试电阻时,所述选定被测试电阻的第二端处的所述测量端由所述第三焊垫组成。

11、进一步的改进是,位于所述电阻串两端的所述被测试电阻分别为第一被测试电阻和最后一个被测试电阻;所述电阻串为环形结构,所述第一个被测试电阻的第一端的所述第一焊垫和所述最后一个被测试电阻的第二端的所述第一焊垫共用。所述电阻串的环形结构中,所述被测试电阻的数量为4个以上,所述第一焊垫的数量等于所述被测试电阻的数量。

12、进一步的改进是,所述第二焊垫和相邻的所述第一焊垫之间通过金属线连接。

13、进一步的改进是,所述第三焊垫和相邻的所述第一焊垫之间通过金属线连接。

14、进一步的改进是,四端法电阻测试结构形成于半导体晶圆上。

15、进一步的改进是,所述四端法电阻测试结构位于所述半导体晶圆的划片道中。

16、进一步的改进是,所述半导体晶圆包括硅晶圆。

17、进一步的改进是,各所述被测试电阻的两个第一焊垫都分别和相邻的所述被测试电阻的第一焊垫共用。

18、进一步的改进是,各所述被测试电阻进行测量时,两个所述激励端用于加激励电流或电压并用于记录或测量电流,两个所述测量端用于测量电压。

19、进一步的改进是,所述激励电流为恒流源电流。

20、进一步的改进是,四端法电阻测试结构作为晶圆允收测试(wat)、仿真电路模拟器(simulation program with integrated circuit emphasis,spice)或可靠性测试中的电阻测试结构。

21、进一步的改进是,所述测试单元中的所述被测试电阻的数量最大值达数十个以上。

22、进一步的改进是,所述四端法电阻测试结构中所述测试单元的数量最大值达数十个以上。

23、和现有技术中,各被测试电阻都需要单独设置4个焊垫来作为4个测试端不同,本发明将被测试电阻串联形成串联结构,各被测试电阻的两端分别设置有一个第一焊垫且至少一个第一焊垫会和相邻的被测试电阻共用,在实际测试中,各被测试电阻依然会有4个测试端,其中被测试电阻两端的第一焊垫作为激励端,测量端能采用和激励端相差一个相邻的被测试电阻的第一焊垫,利用测试时测量端的电流趋于0a,故在测量端和激励端增加一个相邻的被测试电阻并不会影响电压测试结果,但是,却能实现第一焊垫在不同被测试电阻之间的共用,从而能大大减少整个测试单元的焊垫数量,所以,本发明能在保证不影响测试结果的精度的条件下节省焊垫数量并从而节省面积。

技术特征:

1.一种四端法电阻测试结构,其特征在于,包括多条测试单元,各所述测试单元包括:

2.如权利要求1所述的四端法电阻测试结构,其特征在于:所述焊垫还包括第二焊垫和第三焊垫;

3.如权利要求2所述的四端法电阻测试结构,其特征在于:当所述选定被测试电阻为所述第一个被测试电阻时,所述选定被测试电阻的第一端处的所述测量端由所述第二焊垫组成。

4.如权利要求2所述的四端法电阻测试结构,其特征在于:当所述选定被测试电阻为所述最后一个被测试电阻时,所述选定被测试电阻的第二端处的所述测量端由所述第三焊垫组成。

5.如权利要求1所述的四端法电阻测试结构,其特征在于:位于所述电阻串两端的所述被测试电阻分别为第一被测试电阻和最后一个被测试电阻;所述电阻串为环形结构,所述第一个被测试电阻的第一端的所述第一焊垫和所述最后一个被测试电阻的第二端的所述第一焊垫共用,所述电阻串的环形结构中,所述被测试电阻的数量为4个以上,所述第一焊垫的数量等于所述被测试电阻的数量。

6.如权利要求2所述的四端法电阻测试结构,其特征在于:所述第二焊垫和相邻的所述第一焊垫之间通过金属线连接。

7.如权利要求2所述的四端法电阻测试结构,其特征在于:所述第三焊垫和相邻的所述第一焊垫之间通过金属线连接。

8.如权利要求1所述的四端法电阻测试结构,其特征在于:四端法电阻测试结构形成于半导体晶圆上。

9.如权利要求8所述的四端法电阻测试结构,其特征在于:所述四端法电阻测试结构位于所述半导体晶圆的划片道中。

10.如权利要求8所述的四端法电阻测试结构,其特征在于:所述半导体晶圆包括硅晶圆。

11.如权利要求1所述的四端法电阻测试结构,其特征在于:各所述被测试电阻的两个第一焊垫都分别和相邻的所述被测试电阻的第一焊垫共用。

12.如权利要求1所述的四端法电阻测试结构,其特征在于:各所述被测试电阻进行测量时,两个所述激励端用于加激励电流或电压并用于记录或测量电流,两个所述测量端用于测量电压。

13.如权利要求12所述的四端法电阻测试结构,其特征在于:所述激励电流为恒流源电流。

14.如权利要求1所述的四端法电阻测试结构,其特征在于:四端法电阻测试结构作为晶圆允收测试、spice或可靠性测试中的电阻测试结构。

15.如权利要求14所述的四端法电阻测试结构,其特征在于:所述测试单元中的所述被测试电阻的数量最大值达数十个以上。

16.如权利要求14所述的四端法电阻测试结构,其特征在于:所述四端法电阻测试结构中所述测试单元的数量最大值达数十个以上。

技术总结

本发明公开了一种四端法电阻测试结构,测试单元包括:由两个以上被测试电阻串联形成的电阻串,各被测试电阻的两端分别设置有一个第一焊垫,各被测试电阻的两个第一焊垫中的至少一个和相邻的被测试电阻的第一焊垫共用。各被测试电阻都包括两个激励端和两个测量端,两个激励端由被测试电阻的两端的第一焊垫形成以及两个测量端分别由位于对应的激励端相邻位置上的一个焊垫组成。当选定被测试电阻的选定激励端对应的第一焊垫和相邻被测试电阻共用时,选定被测试电阻的和选定激励端相邻的选定测量端由相邻被测试电阻的另一端的第一焊垫组成。本发明能在保证测量精度的条件下节省焊垫数量并从而节省面积。

技术研发人员:蒋昊

受保护的技术使用者:上海华力集成电路制造有限公司

技术研发日:

技术公布日:2024/11/14

技术研发人员:蒋昊

技术所有人:上海华力集成电路制造有限公司

备 注:该技术已申请专利,仅供学习研究,如用于商业用途,请联系技术所有人。

声 明 :此信息收集于网络,如果你是此专利的发明人不想本网站收录此信息请联系我们,我们会在第一时间删除